# An AlGaAs/InGaAs Pseudomorphic HEMT Modulator Driver IC with Low Power Dissipation for 10-Gb/s Optical Transmission Systems

Miyo Miyashita, *Member, IEEE*, Naohito Yoshida, Yoshiki Kojima, Toshiaki Kitano, Norio Higashisaka, *Member, IEEE*, Junichi Nakagawa, *Member, IEEE*, Tadashi Takagi, *Member, IEEE*, and Mutsuyuki Otsubo

**Abstract**—An optical modulator driver integrated circuit (IC) has been developed for 10-Gb/s optical communication systems. To achieve both high-frequency (HF) operation and low power dissipation, 0.2- $\mu$ m T-shaped gate AlGaAs/InGaAs pseudomorphic high-electron-mobility transistors (HEMT's) have been employed for their large transconductance  $g_m$  of 610 mS/mm and high cutoff frequency  $f_T$  of 67.5 GHz. In addition, optimizing input logic swing, switching transistor size in the output driver, and using cascode-current mirror circuits with small output conductance enable power dissipation as low as 1 W to be achieved at a 10-Gb/s nonreturn-to-zero (NRZ) signal output with 3 V<sub>p-p</sub>. This is the lowest value ever reported for power dissipation. As an additional function, the output voltage swing can be controlled in the range from 2 to 3.3 V<sub>p-p</sub> by the current mirror circuit for the purpose of adjusting the optical-output-signal duty factor through an optical modulator.

**Index Terms**—High-speed integrated circuits, integrated circuit design, MODFET integrated circuits, optical communication, optical transmitters.

## I. INTRODUCTION

FOR 10-Gb/s long-haul optical communication systems, transmission systems with external modulation are preferable to direct modulation in terms of suppressing the broadening of spectral linewidth at high bit-rate modulation. The driver integrated circuit (IC) for an electroabsorption (EA)

modulator must normally have both high-speed operation and a large drive voltage to provide the large voltage swing of over 2 V<sub>p-p</sub> required to ensure sufficient extinction ratio at 10 Gb/s [1]. There is also a strong demand for driver IC's with low power dissipation to enable the design of an air-cooled system [2]. Several reports describe large-output driver IC's using high-electron-mobility transistors (HEMT's), heterojunction bipolar transistors (HBT's), and Si-bipolar transistors [3]–[5]. An HEMT IC can operate on a lower supply voltage than HBT or Si-bipolar IC's, so it has the advantage of low power dissipation. For high-speed operation, an HEMT IC usually consists of source-coupled FET logic (SCFL) circuits. In SCFL circuits, reducing power dissipation lessens the internal logic swing and lowers drain-to-source voltage of the switching transistor. The high-frequency (HF) performance of switching transistors must be improved to give a low power dissipation without degradation of switching speed.

The authors' approach has been to adopt 0.2- $\mu$ m-gate AlGaAs/InGaAs pseudomorphic HEMT's for the driver IC. The HEMT's have higher transconductance and cutoff frequency than pseudomorphic 2DEG FET's described in [3], so the driver IC can operate with lower power dissipation. In the circuit design process, the relation between the input logic swing and the gatewidth of the switching transistor was derived to obtain an output of over 3 V<sub>p-p</sub>, thereby optimizing output driver transistor size to make the input logic swing as small as possible. Since current mirror circuits with a cascode configuration are used to provide high impedance current sources, the IC can control the input logic swing using external current sources. These current mirror circuits greatly improve HF performance for single-ended input as well as input logic swing controllability. As a result, the IC is capable of both 3-V<sub>p-p</sub> output and 1-W dissipation with a 10-Gb/s nonreturn to zero (NRZ) signal. The IC can also adjust the output voltage swing from 2 to 3 V<sub>p-p</sub>. This paper describes the device structure, circuit design, and characteristics of the IC.

## II. DEVICE

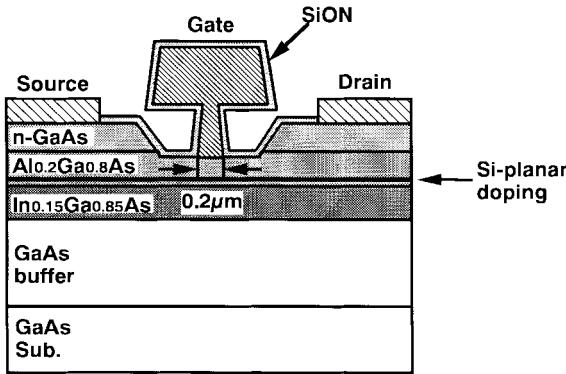

Fig. 1 shows a schematic cross section of the AlGaAs/InGaAs pseudomorphic HEMT. A pH-adjusted citric acid : NH<sub>4</sub>OH:H<sub>2</sub>O<sub>2</sub> solution [6] is used for gate recessing to

Manuscript received October 2, 1996; revised March 24, 1997.

M. Miyashita was with the Optoelectronic and Microwave Devices Laboratory, Mitsubishi Electric Corporation, Itami, Hyogo, 664 Japan. She is now with the Optoelectronics Devices Project Group, High-Frequency and Optical Semiconductor Division, Mitsubishi Electric Corporation, Itami, Hyogo, 664 Japan.

N. Yoshida, N. Higashisaka, and M. Otsubo are with the Optoelectronic and Microwave Devices Laboratory, Mitsubishi Electric Corporation, Itami, Hyogo, 664 Japan.

Y. Kojima and T. Kitano were with the Optoelectronic and Microwave Devices Laboratory, Mitsubishi Electric Corporation, Itami, Hyogo, 664 Japan. They are now with the High-Frequency and Optical Semiconductor Engineering Department, High-Frequency and Optical Semiconductor Division, Mitsubishi Electric Corporation, Itami, Hyogo, 664 Japan.

J. Nakagawa is with the Information Technology Research and Development Center, Mitsubishi Electric Corporation, Kamakura, 247 Japan.

T. Takagi was with the Optoelectronic and Microwave Devices Laboratory, Mitsubishi Electric Corporation, Itami, Hyogo, 664 Japan. He is now with Mitsubishi Electric Corporation, Microwave Electronics Department, Information Technology Research and Development Center, Kamakura, 247 Japan.

Publisher Item Identifier S 0018-9480(97)04455-4.

Fig. 1. Schematic cross section of the AlGaAs/InGaAs pseudomorphic HEMT.

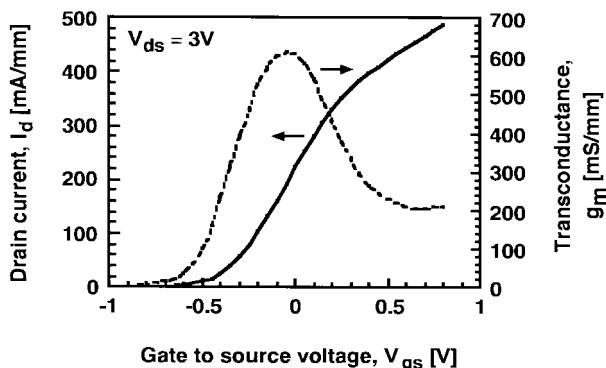

Fig. 2. Drain current and transconductance dependence on gate-to-source voltage of pseudomorphic HEMT.

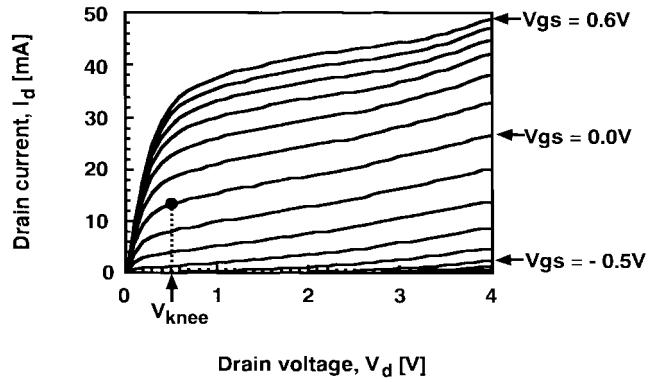

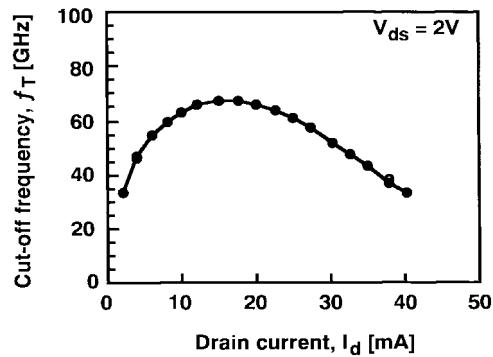

achieve the small deviation of threshold voltage essential to integrated circuits. Fig. 2 shows the dependence of measured drain current  $I_d$  and transconductance  $g_m$  on gate voltage  $V_{gs}$  of the HEMT. When  $V_{gs} \approx 0$  V, the maximum  $g_m$  is as high as 610 mS/mm. Typical threshold voltage is  $-0.8$  V and the gate-to-drain breakdown voltage  $V_{gdo}$  is as high as 10 V. Because of their high electron mobility, HEMT's with low drain-to-source knee voltage  $V_{knee}$  are effective for reducing supply voltage [7]. Fig. 3 shows  $I$ - $V$  characteristics of the HEMT with 100- $\mu$ m-gatewidth. When  $V_{gs} = 0$  V,  $V_{knee}$  is as low as 0.5 V. Fig. 4 shows the characteristics of measured  $f_T$  in terms of  $I_d$  for the 100- $\mu$ m gatewidth HEMT. As can be seen, maximum  $f_T$  is 67.5 GHz. This result is effective for producing lower power dissipation 10-Gb/s driver IC's.

### III. CIRCUIT DESIGN

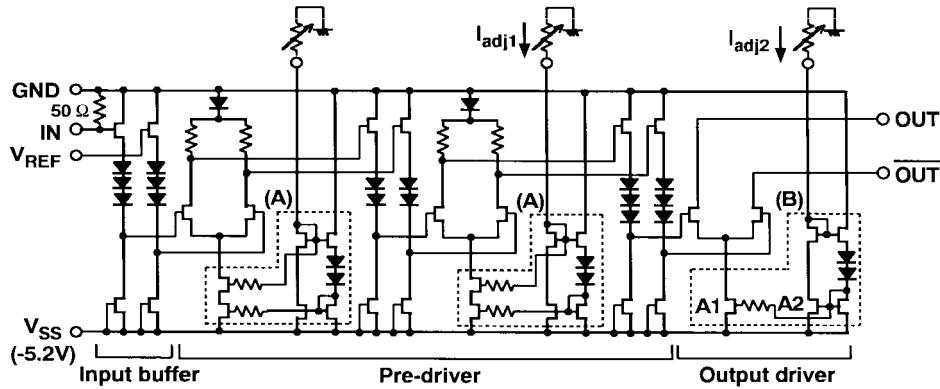

Fig. 5 shows the circuit diagram for the driver IC. The IC consists of an input buffer with an SCFL (0,  $-1$  V) interface, a two-stage differential amplifier acting as a pre-driver, and an output driver. The first stage of the pre-driver provides single-ended to differential conversion. This paper's circuit design target for output voltage swing was 3 V<sub>p-p</sub>. This corresponds to a modulation current of 60 mA<sub>p-p</sub> in the output driver. Increasing the output voltage swing involves increasing the input logic swing of the output driver. In SCFL circuits, however, the maximum input logic swing is limited by supply voltage and drain-to-source knee voltage because differential

Fig. 3.  $I$ - $V$  characteristics of pseudomorphic HEMT.

Fig. 4. Measured  $f_T$  of pseudomorphic HEMT.

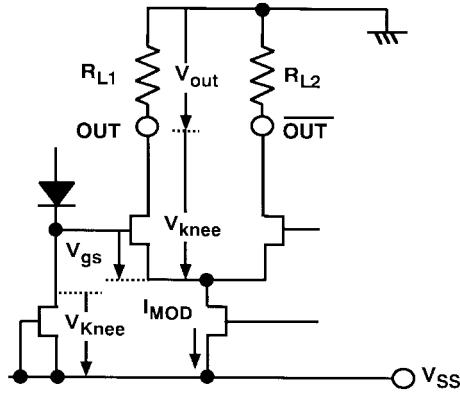

switching transistors must operate in the current saturation region for high-speed operation. For the output driver shown in Fig. 6, the high level  $V_{high}$  and low level  $V_{low}$  of the input logic swing are described by the following formulas:

$$V_{high} \leq -(V_{out} + V_{knee}) + V_{gs\_on} \quad (1)$$

$$V_{low} \geq V_{SS} + V_{knee} \quad (2)$$

where  $V_{out}$  is the output voltage swing required,  $V_{knee}$  is the drain-to-source knee voltage, and  $V_{gs\_on}$  is the gate-to-source voltage necessary to make modulation current  $I_{MOD}$  flow across external load resistor  $R_L$ . The maximum input logic swing  $V_{sw\_max}$  obtained by subtracting  $V_{low}$  from  $V_{high}$  is expressed by

$$V_{sw\_max} = V_{gs\_on} - (V_{out} + V_{SS} + 2 \cdot V_{knee}) \\ = V_{gs\_on} + 1.2. \quad (3)$$

For this IC, parameters  $V_{out}$ ,  $V_{SS}$ , and  $V_{knee}$  are 3.0,  $-5.2$ , and 0.5 V. The switching transistors operate in the current saturation region, so  $V_{gs\_on}$  is given by

$$V_{gs\_on} = \left( \frac{I_{MOD}}{K_u \cdot W_{sw}} \right)^{1/2} + V_{th} \quad (4)$$

where  $K_u$  is the transconductance parameter per-unit gatewidth of 0.68 mA/(V<sup>2</sup> ·  $\mu$ m),  $W_{sw}$  is the gatewidth of the switching transistor, and  $V_{th}$  is the threshold voltage of  $-0.8$  V. From (3) and (4),  $V_{sw\_max}$  for  $W_{sw}$  can be expressed

Fig. 5. Circuit diagram for driver IC.

Fig. 6. Driver circuit diagram for determining the maximum input voltage swing.

as follows:

$$V_{sw\_max} = \left( \frac{I_{MOD}}{K_u \cdot W_{sw}} \right)^{1/2} + V_{th} + 1.2 \approx \left( \frac{90}{W_{sw}} \right)^{1/2} + 0.4. \quad (5)$$

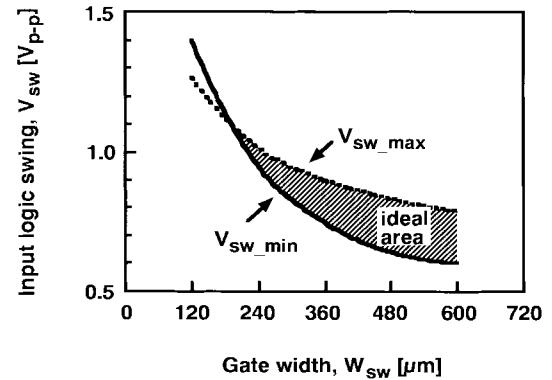

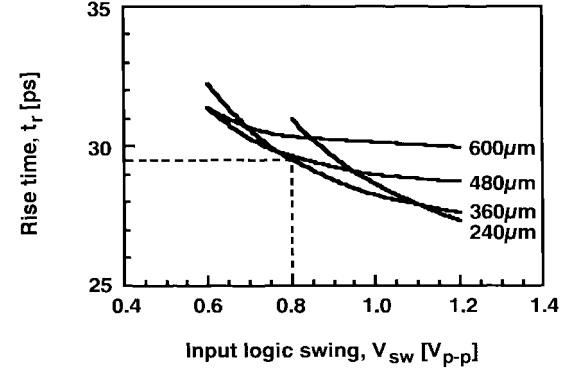

In Fig. 7,  $V_{sw\_min}$  and  $V_{sw\_max}$  are plotted against  $W_{sw}$ , where  $V_{sw\_min}$  (shown by a solid line) is the simulated input logic swing necessary for achieving output voltage swing of 3 V<sub>p-p</sub> at least, and  $V_{sw\_max}$  (shown by a dotted line) is estimated by (5). In the simulation of the output driver, the authors' considered that the parasitic capacitance connected in parallel with a 50-Ω load resistor, which includes on-chip metallization-line capacitance and the pad capacitance, was 0.3 pF. In this design, both  $V_{sw}$  and  $W_{sw}$  are optimized within the ideal area shown by oblique lines in Fig. 7, because the output voltage swing is smaller than 3 V<sub>p-p</sub> under the condition of  $V_{sw}$  below  $V_{sw\_min}$  and the switching speed is not improved under the condition of  $V_{sw}$  above  $V_{sw\_max}$ . For the switching speed, the relation between  $V_{sw}$  and  $W_{sw}$  shown in Fig. 8 is also important [8]. Rise time at the output terminal of the output driver  $t_r$  decreases as the input logic swing increases, and this decrease is larger as  $W_{sw}$  becomes smaller. From Fig. 8, one can see that a  $W_{sw}$  of 360 μm can give the fastest  $t_r$  for a lower input logic swing. In this paper, a  $W_{sw}$  of 360 μm and a  $V_{sw}$  of 0.8 V<sub>p-p</sub> were determined in consideration of the switching speed and the relation shown in Fig. 7.

Fig. 7. Minimum and maximum input logic swing against the gatewidth of the switching HEMT.

Fig. 8. Rise time at output terminal dependence on the input logic swing.

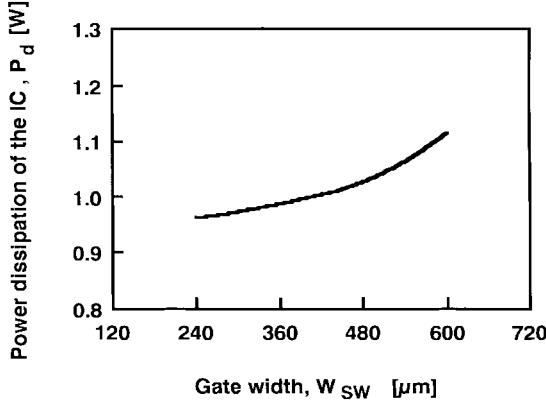

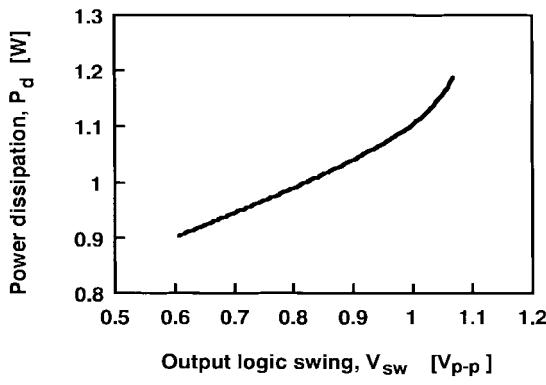

Because  $W_{sw}$  and  $V_{sw}$  also influence power dissipation of the IC  $P_d$ , the authors discuss the relation between both  $P_d$  and  $W_{sw}$ , and  $P_d$  and  $V_{sw}$ . The increase in  $W_{sw}$  involves the increase in the parasitic capacitance loaded for the pre-driver. The decrease in  $t_r$  increases the currents flowing through the source followers of the pre-driver as well as input logic swing, indicating that the  $P_d$  is deeply related to the driverability of the pre-driver, which makes  $t_r$  fast. In Fig. 9, the  $P_d$  for different  $W_{sw}$  was simulated, where the currents flowing through the source followers and  $V_{sw}$  were optimized so that  $t_r$  keeps 30 ps. Over a  $W_{sw}$  of 480 μm, the  $P_d$  is rapidly increased. The  $V_{sw}$  also depends on the  $P_d$ . The  $P_d$  as a function of  $V_{sw}$  is shown in Fig. 10. In this

Fig. 9. Power dissipation of the IC for the different gatewidth of the switching transistor.

Fig. 10. Power dissipation of the IC as a function of the output logic swing of the pre-driver.

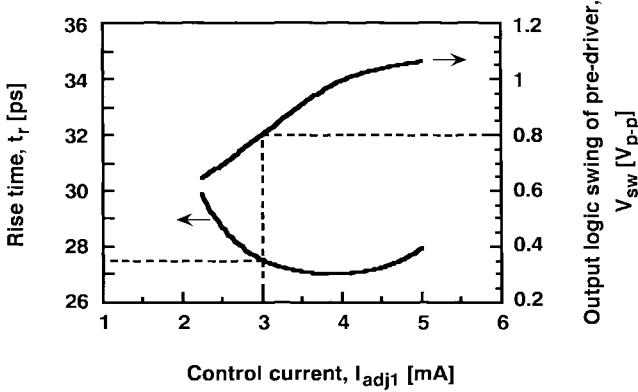

Fig. 11. Rise time at output terminal of the output driver and the output logic swing of pre-driver dependence on the control current  $I_{adj1}$ .

simulation, the  $V_{sw}$  is increased by the currents dissipated in the differential pair transistors of the pre-driver because the increase in load resistance degrades frequency response of the pre-driver. Fig. 10 shows  $P_d$  increases as  $V_{sw}$  increases. Thus, it is essential that both  $W_{sw}$  and  $V_{sw}$  are optimized as small as possible for reducing  $P_d$ . The  $W_{sw}$  of 360  $\mu\text{m}$  and  $V_{sw}$  of 0.8 V<sub>p-p</sub> utilized in this paper are sufficiently small to reduce  $P_d$ .

To obtain both the high-speed and large voltage output characteristics, the output logic swing of the pre-driver needs to be precisely controlled. A current mirror circuit (*A*) with

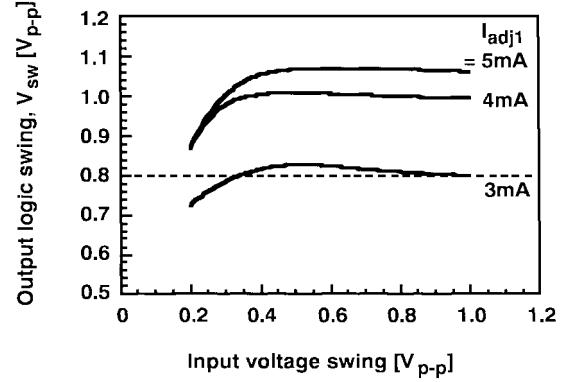

Fig. 12. The output logic swing of pre-driver dependence on the input voltage swing of the IC for different control current  $I_{adj1}$ .

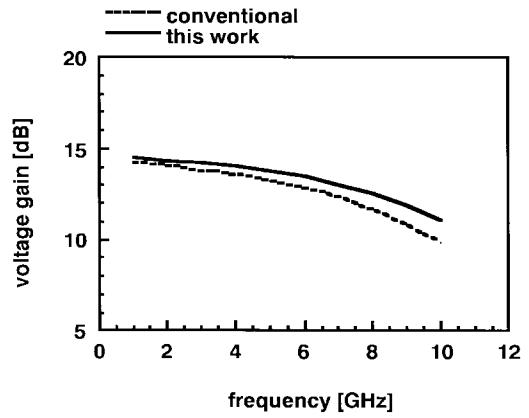

Fig. 13. Frequency response of the pre-driver.

a cascode configuration is adopted as the current source for each differential stage of the pre-driver. This reduces changes in the internal logic swing due to supply voltage variations. The output logic swing of the pre-driver is adjusted by external current source  $I_{adj1}$  as shown in Fig. 11. When  $I_{adj1} = 3\text{ mA}$ , the output logic swing is 0.8 V<sub>p-p</sub>, leading to a  $t_r$  of 27.5 ps. As can be seen from Fig. 12, a pre-driver with a high gain of 14 dB keeps the output logic swing constant over a change in the single input signal from 0.4 to 1 V<sub>p-p</sub>.

Another merit of using the current mirror circuit (*A*) will now be mentioned. The voltage gain of the pre-driver is very affected by the output conductance of the current sources since the pre-driver operates with single-ended input. In Fig. 13, the simulated voltage gain of the pre-driver in the IC is compared with that of conventional circuit such as the current mirror circuit (*B*). Because the output conductance of the current source in this paper is very small, in spite of large drain conductance of the HEMT, the loss of the voltage gain is extremely small. The SPICE transient analysis shows that the difference of the voltage gain shown in this paper and a conventional circuit corresponds to the difference of the output voltage swing of 0.1 V<sub>p-p</sub> at pre-driver output. As expected from Figs. 7 and 8, the decrease in the output voltage swing causes degradation of rise time or output voltage swing at the output terminal of the IC. This degradation in the conventional circuit leads to the increase of  $P_d$ , even though it would be compensated by an increase in the internal logic swing. In

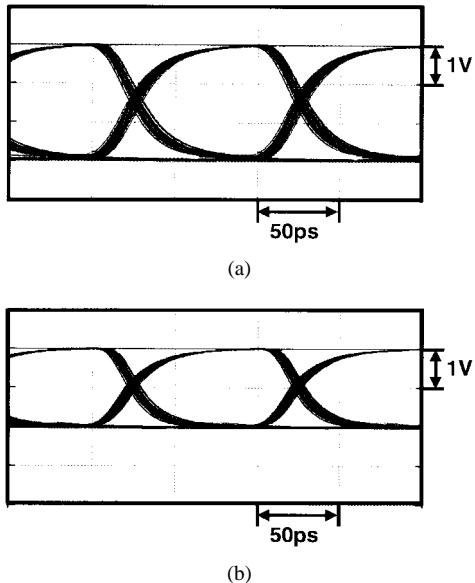

Fig. 14. Simulated output diagram at 10-Gb/s,  $2^7 - 1$  PRBS for different control currents  $I_{adj2}$ . (a)  $I_{adj2} = 3.5$  mA and (b)  $I_{adj2} = 2.0$  mA.

Fig. 15. Microphotograph of driver IC.

this paper's circuit, utilization of the current mirror circuit (*A*) saves the  $P_d$  of about 50 mW as shown in Fig. 10.

The output driver also includes a current mirror circuit (*B*). The output voltage swing is controlled by the current mirror circuit in order to adjust the duty factor of the optical output signal through an optical modulator, which has nonlinear characteristics for optical power versus input voltage. The ratio of gatewidth of  $A_1$  to  $A_2$  is set at 16:1 to make control current  $I_{adj2}$  small. Another merit of utilizing a current mirror circuit is that output voltage variations according to supply voltage or ambient temperature can be compensated for using an external bias control circuit [9]. Fig. 14 shows output simulations for different values of the control current  $I_{adj2}$  at 10 Gb/s. The 1-V<sub>p-p</sub> input signal is a pseudo-random bit sequence (PRBS) of  $2^7 - 1$ . When  $I_{adj2} = 3.5$  mA, the output voltage swing is 3 V<sub>p-p</sub>. The minimum output voltage swing is 2 V<sub>p-p</sub> when  $I_{adj2} = 2.0$  mA.

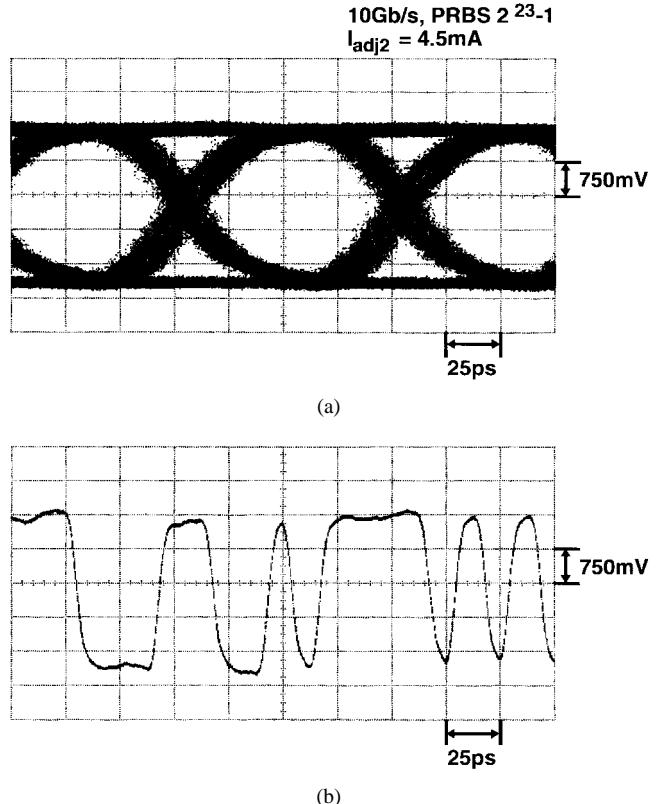

Fig. 16. (a) Measured output diagram and (b) section of the output pulse sequence for output voltage swing of 3.3 V<sub>p-p</sub> at 10 Gb/s.

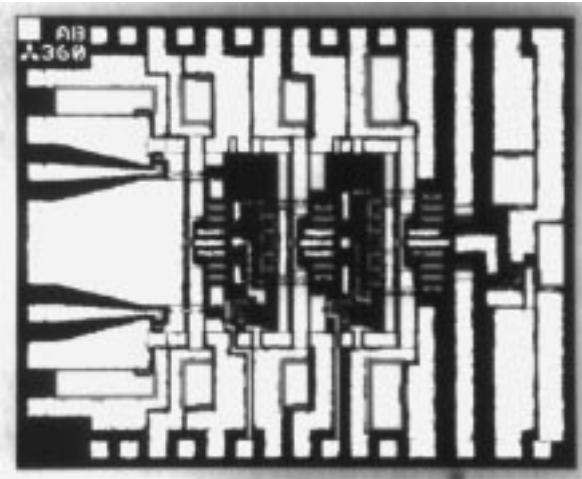

Fig. 15 is a microphotograph of the driver IC. A coplanar structure with 50- $\Omega$  impedance is employed for the input and output lines. Both  $IN$  and  $V_{REF}$  terminals can be terminated to ground by on-chip 50- $\Omega$  resistors to allow differential input. Metal-insulator-metal capacitors are integrated as bypass capacitors to stabilize the power supplies at -5.2 V. Chip size is 3.0 mm  $\times$  2.5 mm.

#### IV. CHARACTERISTICS

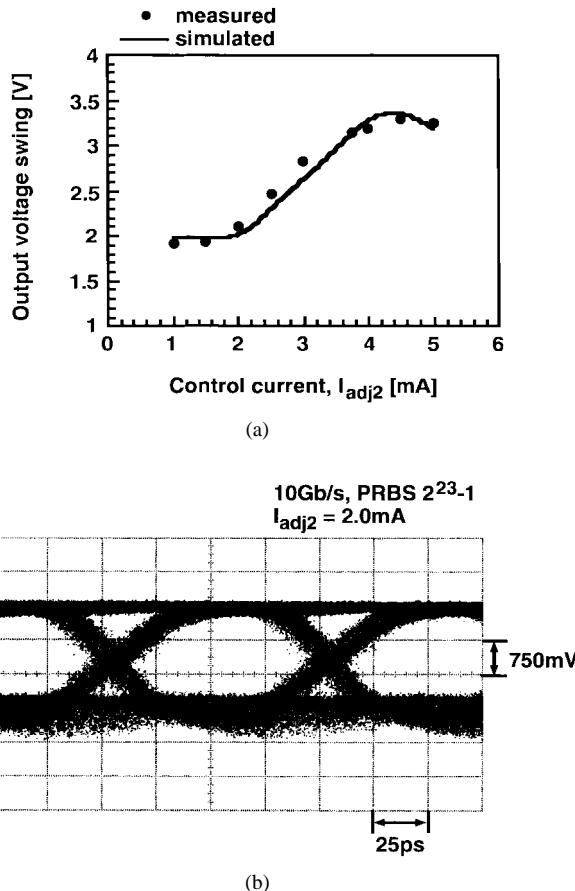

The IC was assembled on a ceramic carrier and measured in 50- $\Omega$  testing systems. Fig. 16 shows the output diagram and a section of the output pulse sequence for SCFL input with PRBS of  $2^{23} - 1$  when the IC is driving a 50- $\Omega$  load. The maximum voltage swing of 3.3 V<sub>p-p</sub> and rise/fall times (20%-80%) of 32.4/30.2 ps are obtained at 10 Gb/s. Good eye opening is observed and sensitivity for the input voltage swing in single-input operation is as low as 0.4 V<sub>p-p</sub>. Fig. 17 shows the measured and simulated output voltage swing dependence on the control current  $I_{adj2}$  shown in Fig. 5, and the output diagram for the minimum output voltage swing when  $I_{adj2} = 2.0$  mA. The output diagram is well opened and has no edge-steepness degradation. The output voltage swing changes from 2 to 3 V<sub>p-p</sub> in proportion to  $I_{adj2}$ , a range which is more than sufficiently wide for adjusting the duty factor of the optical output signal through an optical modulator. Measurements agree well with the simulations. The power dissipation for 3 V<sub>p-p</sub> output voltage swing is 1.0 W, the lowest value ever reported [2]-[4].

Fig. 17. Measured and simulated output voltage swing dependence on the control current (a)  $I_{adj2}$  and the output diagram at (b)  $I_{adj2}$  of 2.0 mA.

## V. CONCLUSION

A modulator driver IC using 0.2- $\mu$ m-gate AlGaAs/InGaAs HEMT's has been developed for 10-Gb/s optical transmission systems. Despite the large output voltage swing of 3 V<sub>p-p</sub>, the IC has power dissipation of only 1 W. The driver IC will contribute to the construction of 10-Gb/s long-haul optical communication systems.

## ACKNOWLEDGMENT

The authors express their sincere thanks to K. Motoshima and T. Kitayama for continuous encouragement. Special thanks goes to K. Yamamoto for his valuable suggestions and technical discussions.

## REFERENCES

- [1] Y. Miyazaki *et al.*, "Novel current-blocking structure for high-speed EA-modulator/DFB-LD integrated light source," in *IOOC-95 Tech. Dig.*, vol. 4, Hong Kong, June 1995, pp. 60-61.

- [2] N. Higashisaka *et al.*, "GaAs DCFL 2.5-Gbps 16-bit multiplexer/demultiplexer," *IEEE J. Solid-State Circuits*, vol. 29, pp. 808-814, July 1994.

- [3] Y. Suzuki *et al.*, "Pseudomorphic 2DEG FET IC's for 10-Gb/s optical communication systems with external optical modulation," *IEEE J. Solid-State Circuits*, vol. 27, pp. 1342-1346, Oct. 1992.

- [4] R. K. Montgomery *et al.*, "10-Gbit/s AlGaAs/GaAs HBT driver IC for lasers or lightwave modulators," *IEEE Electron Device Lett.*, vol. 27, pp. 1827-1829, Sept. 1991.

- [5] H.-M. Rein *et al.*, "A versatile Si-bipolar driver circuit with high output voltage swing for external and direct laser modulation in 10-Gb/s optical-fiber links," *IEEE J. Solid-State Circuits*, pp. 1014-1021, Sept. 1994.

- [6] T. Kitano *et al.*, "Selective etching of GaAs/Al<sub>x</sub>Ga<sub>1-x</sub>As for heterostructure field effect transistors," in *Symp. SOTAPCOCS XXIII Tech. Dig.*, Oct. 1995, vol. 95-21, pp. 327-336.

- [7] M. Fujii *et al.*, "An ultra low-power AlGaAs/InGaAs HJFET SCFL circuit for 10-Gbps applications with 1.3-V supply voltage," in *IEEE Dig. GaAs IC Symp.*, Philadelphia, PA, Oct. 1994, pp. 51-54.

- [8] K. Ishikawa *et al.*, "A large-output optical modulator driver-IC for 10-Gb/s optical transmission systems," in *Proc. IEICE General Conf.*, Sendai, Japan, Sept. 1994, C-433.

- [9] M. Miyashita *et al.*, "A GaAs LD driver IC for 2.5 Gb/s optical communication system," in *24th European Microwave Conf. Proc.*, vol. 2, Cannes, France, Sept. 1994, pp. 1649-1654.

**Miyo Miyashita** (M'97) was born in Hyogo, Japan, on October 11, 1964. She received the B.S. degree in physics from Kwansei-Gakuin University, Hyogo, Japan, in 1987.

In 1987, she joined the LSI Research and Development Laboratory, Mitsubishi Electric Corporation, Itami, Hyogo, Japan. From 1989 to 1997, she was a Technical Staff Member in the Microwave Device Development Department, Optoelectronic and Microwave Devices Laboratory (OML). In 1997, she moved from the OML to the Optoelectronics Devices Project Group in the High-Frequency and Optical Semiconductor Division, where she is currently a Technical Staff Member.

Ms. Miyashita is a member of the Institute of Electronics, Information, and Communication Engineers of Japan.

**Naohito Yoshida** was born in Hyogo, Japan, on December 16, 1958. He received the B.E., M.E., and Ph.D. degrees from Nagoya Institute of Technology, Nagoya, Japan, in 1981, 1983, and 1996, respectively.

In 1983, he joined the LSI Research and Development Laboratory, Mitsubishi Electric Corporation, Itami, Hyogo, Japan, and has been engaged in the research and development of optical and microwave devices. He is currently developing HEMT's for microwave and millimeter-wave application at the Optoelectronic and Microwave Devices Laboratory (OML), Mitsubishi Electric Corporation.

Dr. Yoshida is a member of the Japan Society of Applied Physics and the Institute of Electronics, Information, and Communication Engineers.

**Yoshiki Kojima** was born in Aichi, Japan, in 1969. He received the B.S. degree in applied electronic communication from Musashi Institute of Technology, Tokyo, Japan, in 1991.

In 1991, he joined the Optoelectronic and Microwave Devices Laboratory (OML), Mitsubishi Electric Corporation, Itami, Hyogo, Japan, as a Technical Staff Member. He is currently a Technical Staff Member in the High-Frequency and Optical Semiconductor Engineering Department of the High-Frequency and Optical Semiconductor Division. He has been engaged in the development of lithography for GaAs IC's.

**Toshiaki Kitano** was born in Osaka, Japan, in 1964. He received the B.S. and M.S. degrees in applied chemistry from Osaka University, Osaka, Japan, in 1988 and 1990, respectively.

In 1990, he joined the Optoelectronic and Microwave Devices Laboratory (OML), Mitsubishi Electric Corporation, Itami, Hyogo, Japan. He has been engaged in the development of dry and wet etching technology for GaAs IC's. In 1996, he moved from the OML to the High-Frequency and Optical Semiconductor Engineering Department in the High Frequency and Optical Semiconductor Division, where he is currently a Technical Staff Member.

**Norio Higashisaka** (M'92) was born in Hyogo, Japan, in 1960. He received the B.S. degree in physics from Kobe University, Hyogo, Japan, in 1983.

In 1983, he joined LSI Research and Development Laboratory, Mitsubishi Electric Corporation, Itami, Hyogo, Japan, where he had been engaged in research and development of ECL gate arrays. Since 1991, he has worked on the research and development of GaAs LSI's in Mitsubishi Electric Corporation's Optoelectronic and Microwave Devices Laboratory (OML). His research interests include high-speed low-power circuits for communication system and data processing, device modeling, and HF measurement technology.

**Junichi Nakagawa** (S'67-M'68) was born in Osaka, Japan, on August 31, 1965. He received the B.S., M.S., and Ph.D. degrees in electrical engineering from the University of Tokyo, Tokyo, Japan, in 1989, 1991, and 1994, respectively.

In 1994, he joined the Mitsubishi Electric Corporation, Kamakura, Japan, where he has been engaged in the research and development of high-speed GaAs IC's and high-speed optical fiber transmission systems. He is currently a Technical Staff Member in the Information Technology Research

and Development Center.

Dr. Nakagawa is a member of the Institute of Electronics, Information, and Communication Engineers of Japan.

**Tadashi Takagi** (M'92) received the B.S. degree in physics from Tokyo Institute of Technology, Tokyo, Japan, in 1973, and the Ph.D. degree in electronic engineering from Shizuoka University, in 1995.

In 1973, he joined the Mitsubishi Electric Corporation, Itami, Hyogo, Japan, where he has been engaged in the research and development of microwave and millimeter-wave monolithic integrated circuits (MMIC's) and solid-state power amplifiers (SSPA's). He is currently the Section Manager of Mitsubishi Electric Corporation's Microwave Electronics Department, Information Technology Research and Development Center, Kamakura, Japan.

**Mutsuyuki Otsubo** was born in Tottori, Japan. He received the M.S. and Ph.D. degrees in electronic engineering from Tohoku University, Sendai, Japan, in 1969 and 1976, respectively.

In 1969, he joined the Mitsubishi Electronic Corporation, Itami, Hyogo, Japan, where he worked in the development of compound semiconductor epitaxial technology for the microwave applications. From 1975 to 1980, he was responsible for the development of GaAs field-effect transistors. From 1981 to 1992, he was the Manager of the Microwave Devices Development Department, responsible for GaAs integrated-circuits development. From 1993 to 1995, he was the Manager of the Optoelectronic Devices Development Department, Optoelectronic and Microwave Devices Laboratory (OML). Since 1995, he has been the Manager of the Microwave Devices Department, OML.